## Development of solid state amplifiers at ESRF

#### Cavity combiner prototype

#### **Michel Langlois**

\* This work, carried out within the framework of the CRISP project, has received research funding from the EU Seventh Framework Programme, FP7.

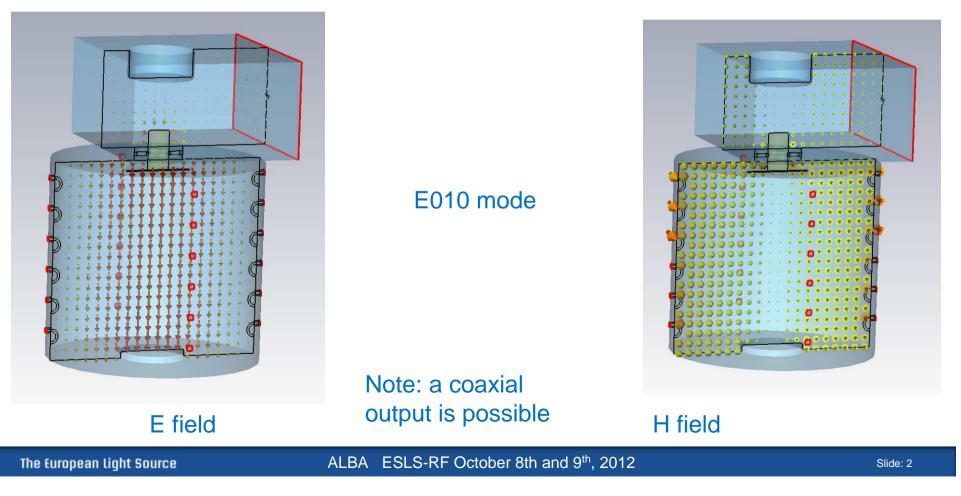

## RF combining : the cavity combiner

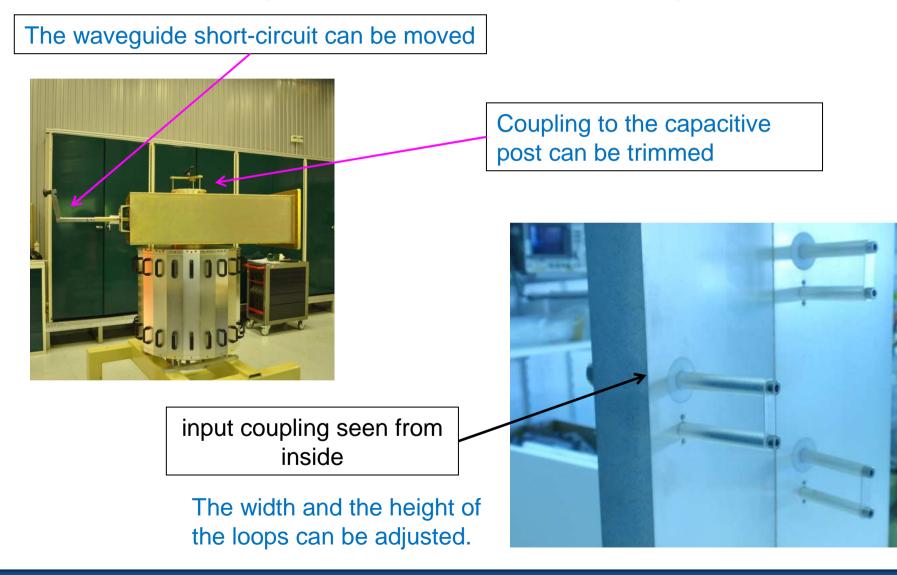

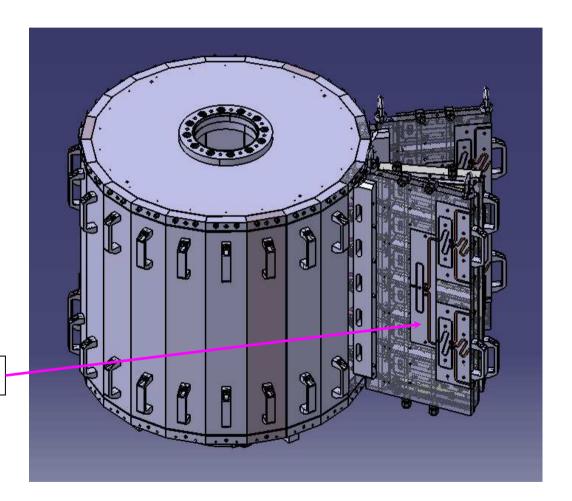

We developed a cavity combiner which could couple up to 132 RF modules. Input coupling is provided by loops on the periphery. Output coupling is capacitive and excite the fundamental rectangular waveguide mode.

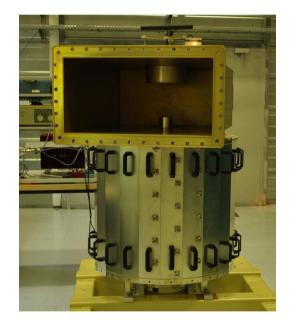

## Cavity combiner: the prototype

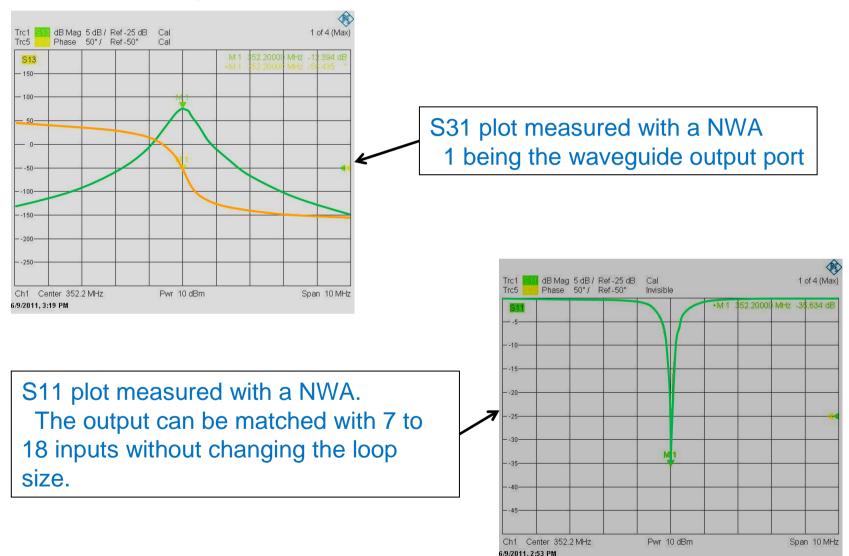

## cavity combiner: low level results

## Cavity combiner: issues

>The behaviour with power has not yet been tested.

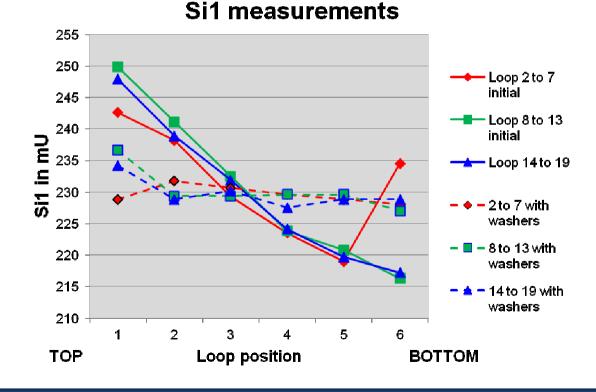

There is a discrepancy on S1i, depending on the i loop

position. The loop size must vary with position.

We adjusted washers on the loops to vary their heights and got close values for all S<sub>i1</sub>

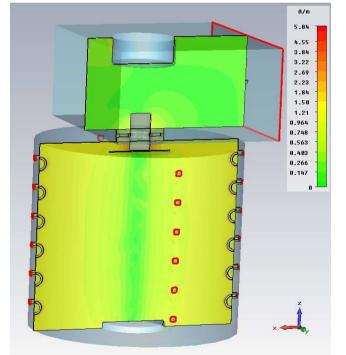

#### The cavity combiner : losses

#### Theory:

Most of the losses are due to the current in the cylindrical wall. We computed 1.35 kW for 75 kW output (conductivity:5\*10<sup>7</sup> S/m). It does not depend heavily on the number of input loops. It means 0.08 dB insertion loss.

Low level measurements:

$$\left|\sum_{i=2}^{19} S_{i,1}\right| = \sqrt{17.23}$$

The theoretical value would be  $\sqrt{18}$

A dubious contact was seen on the movable short circuit, but straightening the waveguide sagging did not change  $\Sigma S_{1,i}$ .

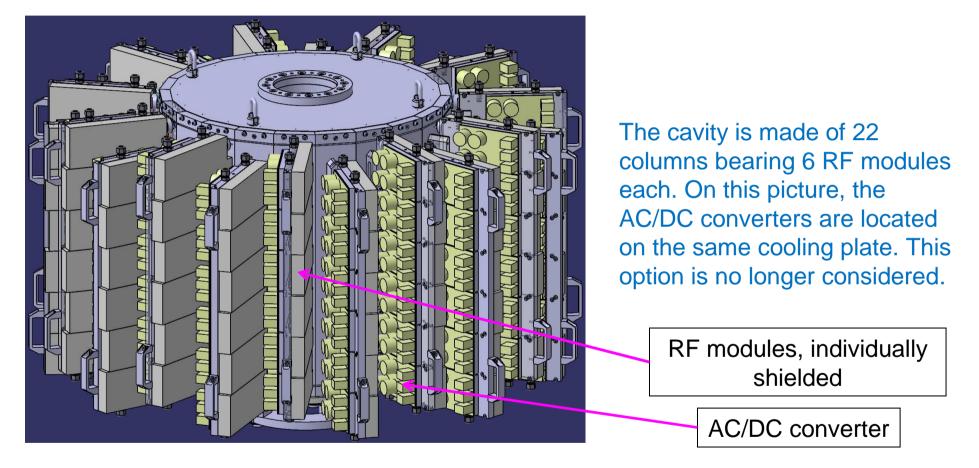

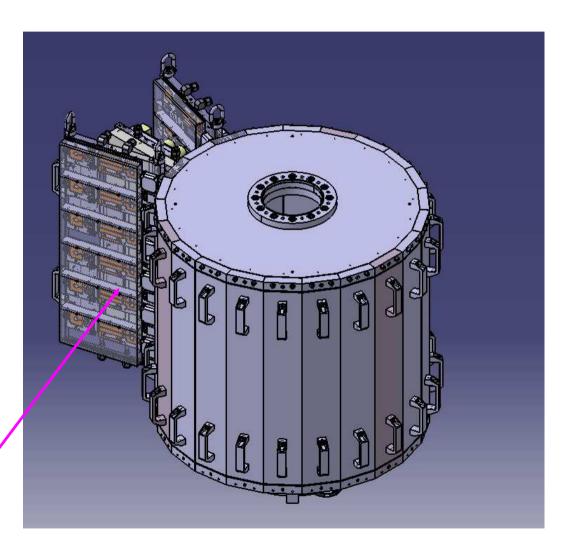

#### cavity combiner: modules implementation

The wings constitute the cylindrical cavity wall

### Cavity combiner: modules implementation

For the 10kW first step, the cavity is fitted with 3 adjacent (or not) "wings". Each of them is equipped with 6 transistor amplifiers. They are all water cooled. The water feeding circuit has not been designed yet. It cannot use the ESRF deionized water circuit, because aluminum is forbidden on this loop.

RF modules globally shielded

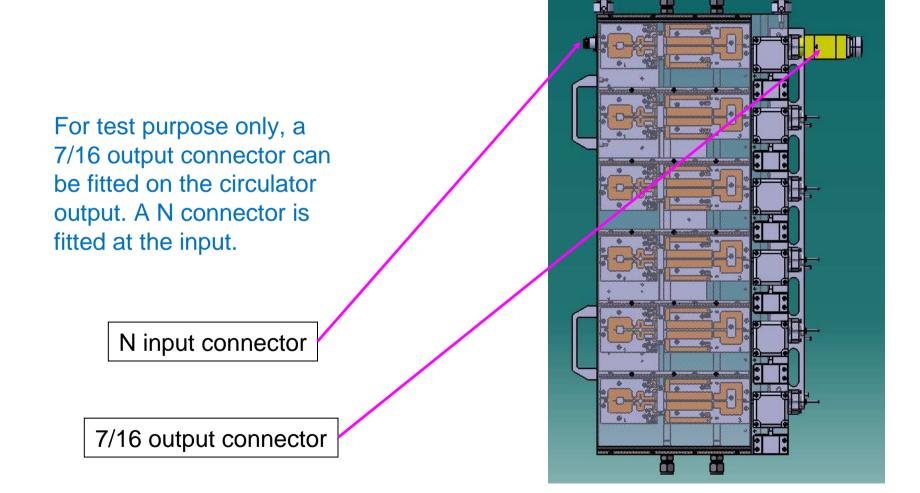

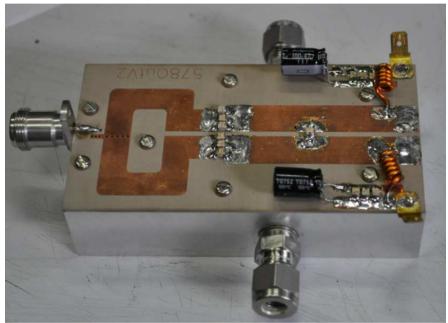

#### Cavity combiner: test fixture

#### Cavity combiner: RF distribution

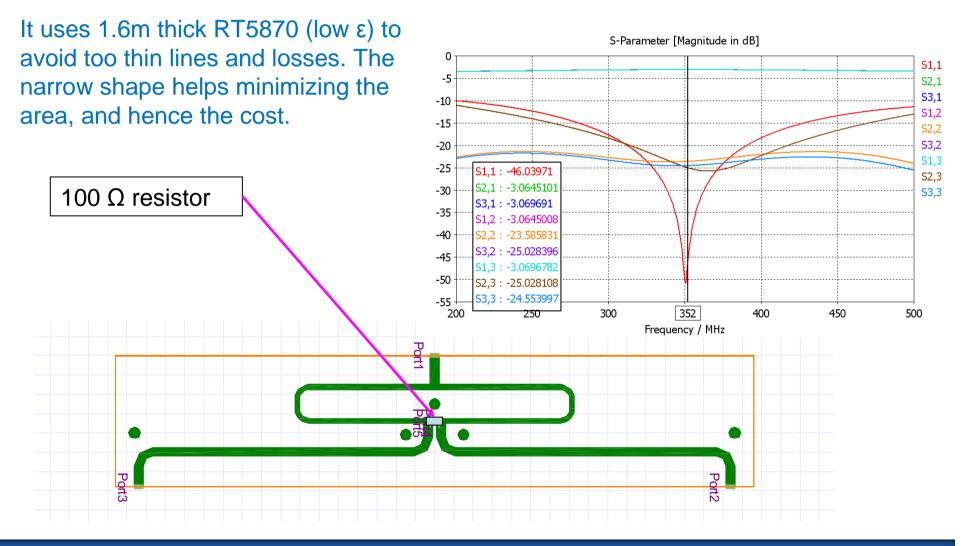

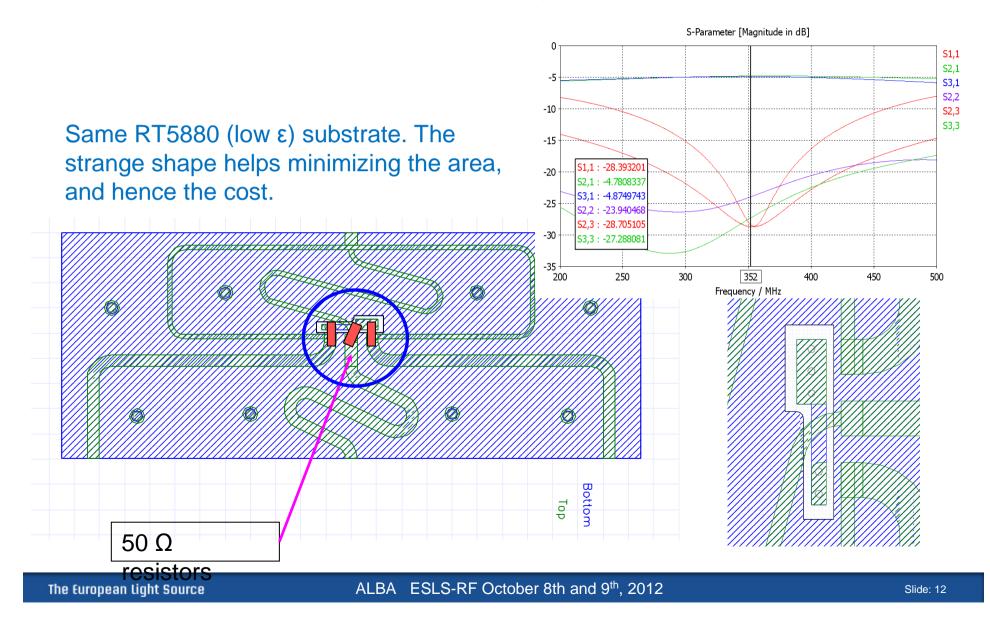

RF distribution is made with printed Wilkinson dividers to avoid connectors and cables. The 2 ways splitter is a delta Wilkinson, and the 3 ways is star connected.

**RF** distribution

## Cavity combiner: 2 ways Wilkinson divider

#### Cavity combiner: 3 ways Wilkinson star divider

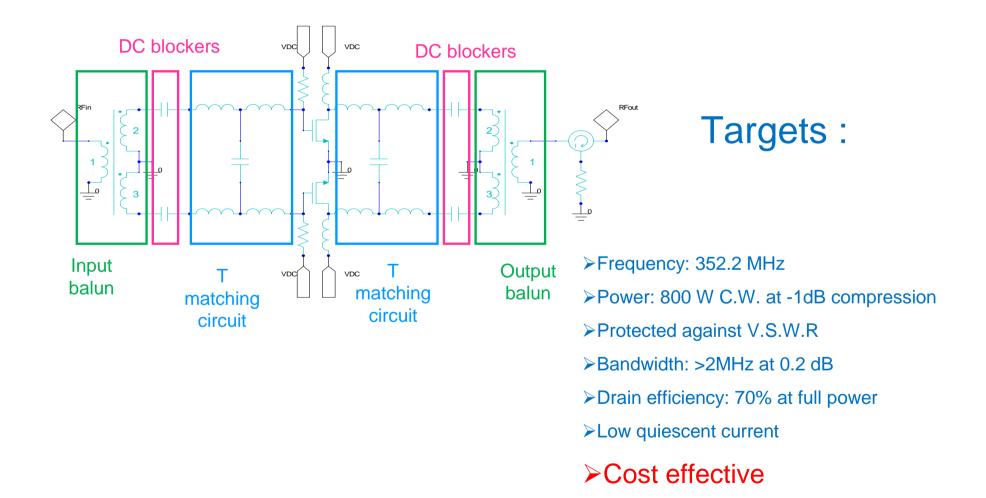

### The RF module: Scheme

## The RF module: design options

Avoidance of components needing manual intervention

No variable capacitors

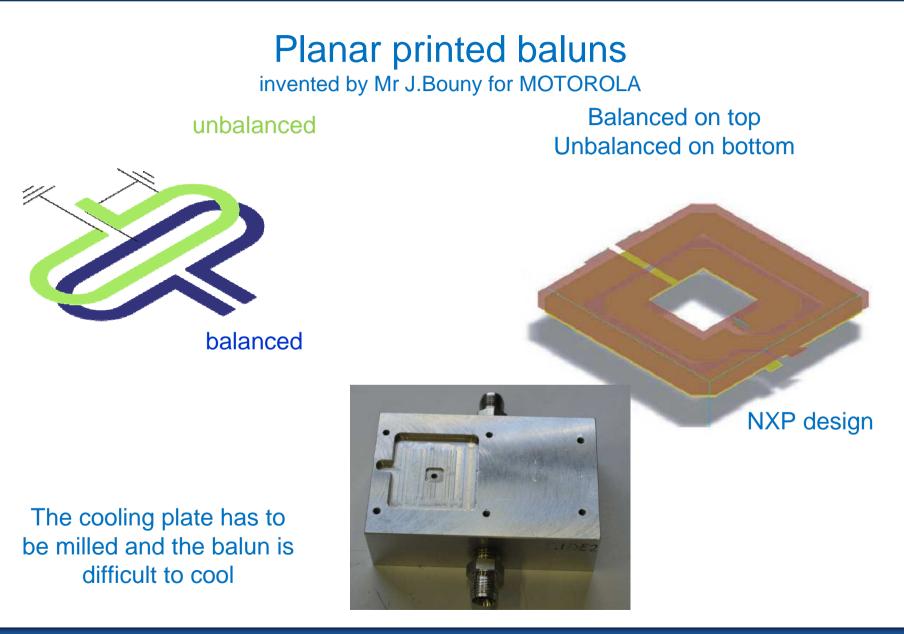

Suspended printed planar baluns

No trimmer except for gate bias

No RF chokes

Transistor choice: LDMOS 50V

≻NXP BLF578

FREESCALE MRF6VP41KH

Ruggedized version of the formers

Accelerator & Source Division Day

### The RF module: input

V1

The input circuit printed circuit was OK from the start. The 2<sup>nd</sup> version has two bias voltage sources made from the drain voltage.

V3

### The RF module: output

V1 Substrate  $\lambda$ =0.24W/m\*K

Overheating of the output balun and its matching capacitors.

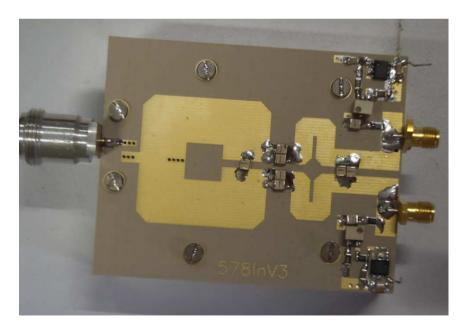

#### The RF module output circuit: 578OutV21

V21 High conductivity substrate No capacitor on the balun

#### The RF module output circuit: 578V3V3

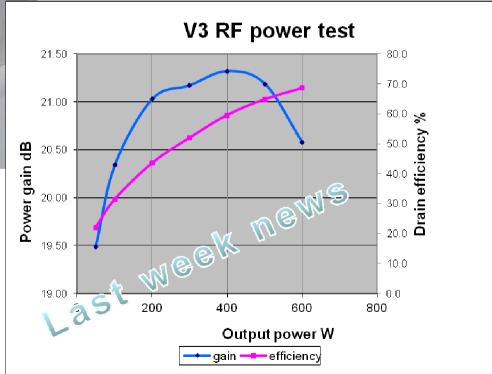

#### V3

RF drain chokes have been replaced with "quarter wave" transmission lines. Very few components are left, all of them CMS and prone to automated manufacturing in Europe.

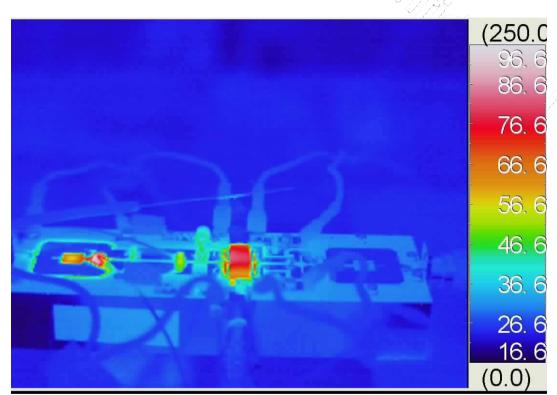

## The RF module: issues

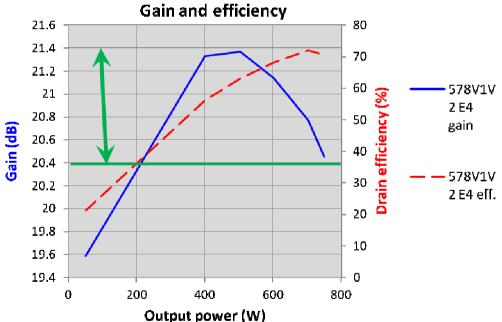

≻The results shown were obtained with the NXP transistor. It has to be repeated with the FREESCALE MOSFET.

➤The power limitation comes from the transistor ESD protection diode, which conducts as soon as the input power reaches 6.4 W. This is probably the reason for the early saturation of the V3 version. The XR ruggedized version should not exhibit this drawback.

>The reproducibility has not been checked yet.

≻The output matching capacitor is hot. Long runs have to be performed to make sure these temperatures are acceptable.

## 578V3V3 : prices

Bill of material:

For 20 modules, transistor and circulator included, 487€/module

For 150 modules, transistor and circulator included, 382€/module

### Many thanks!

# •To my colleagues of both the RF group and the design office, for their support.

•To Francis PEREZ (ALBA) who first dared to test the cavity combiner concept to combine 2 IOTs.